|

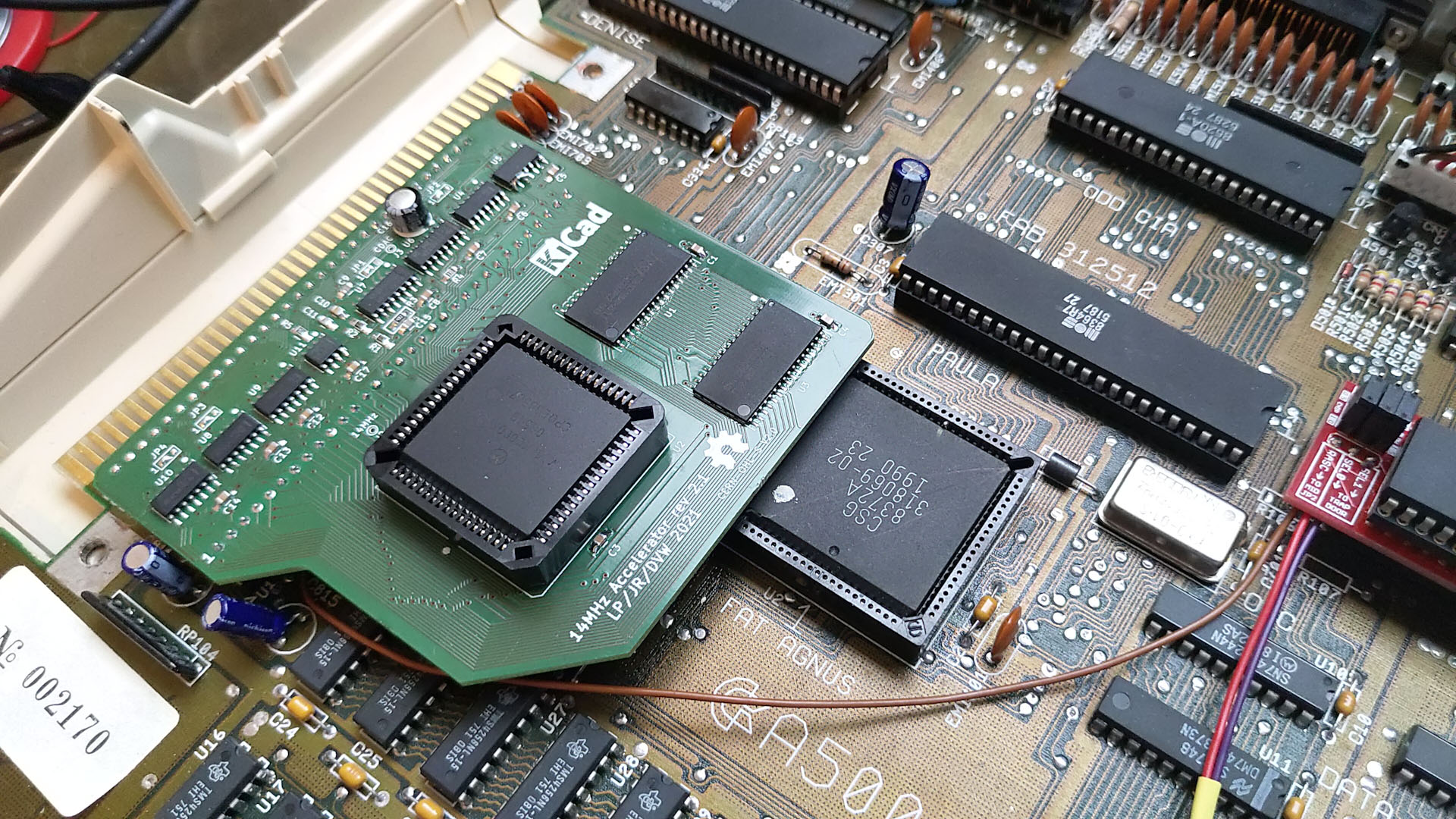

Open source 14MHz 68000 accelerator

This is a 14MHz 68000 accelerator with 1MB fast ram and disable switch for the Amiga.

The main attraction of this design is that it uses no programmable logic. Only standard 7400 & 4000 logic.

Tested on a rev. 5 Amiga 500. It might also work on other revisions and Amiga models but that has not been tested. The design is licensed under CERN OHL-S V2.0 The design is a complete overhaul of a design by Livio Plos and Jorg Richter.

All files can be found on github here: https://github.com/Mathesar/14mhz-accelerator

Changes include:

- New clock doubler using an old school 4046 PLL to generate the 7MHz quadrature clock.

This is more reliable than the RC delays in the original design. Alternatively the quadrature clock can be taken from the motherboard. The latter has not been tested

- an optional 1Mb of zero waitstate Ranger RAM has been added to take full advantage of the 14MHz cpu.

- an optional reset timing based switch has been added to disable the ranger RAM upon boot.

Variants

The accelerator can be build in 3 variant:

- Accelerator only This only doubles the clock of the CPU to 14MHz.

- Accelerator plus 1MB zero waitstate ranger RAM The above but adds 1MB of fast RAM. This makes the accelerator about 2.7 times faster than a stock A500

- Accelerator plus 1MB zero waitstate ranger RAM plus disable circuit The above but adds a timer based disable option for the RAM. By holdiing ctrl-amiga-amiga down for more than 5..6 seconds the RAM is disabled.

It is enabled again on the next (less than 5..6 seconds) reset cycle

And this is how it looks  :

Moved from the previous thread here: http://eab.abime.net/showthread.php?t=97512

Last edited by Mathesar; 03 July 2021 at 21:55.

|